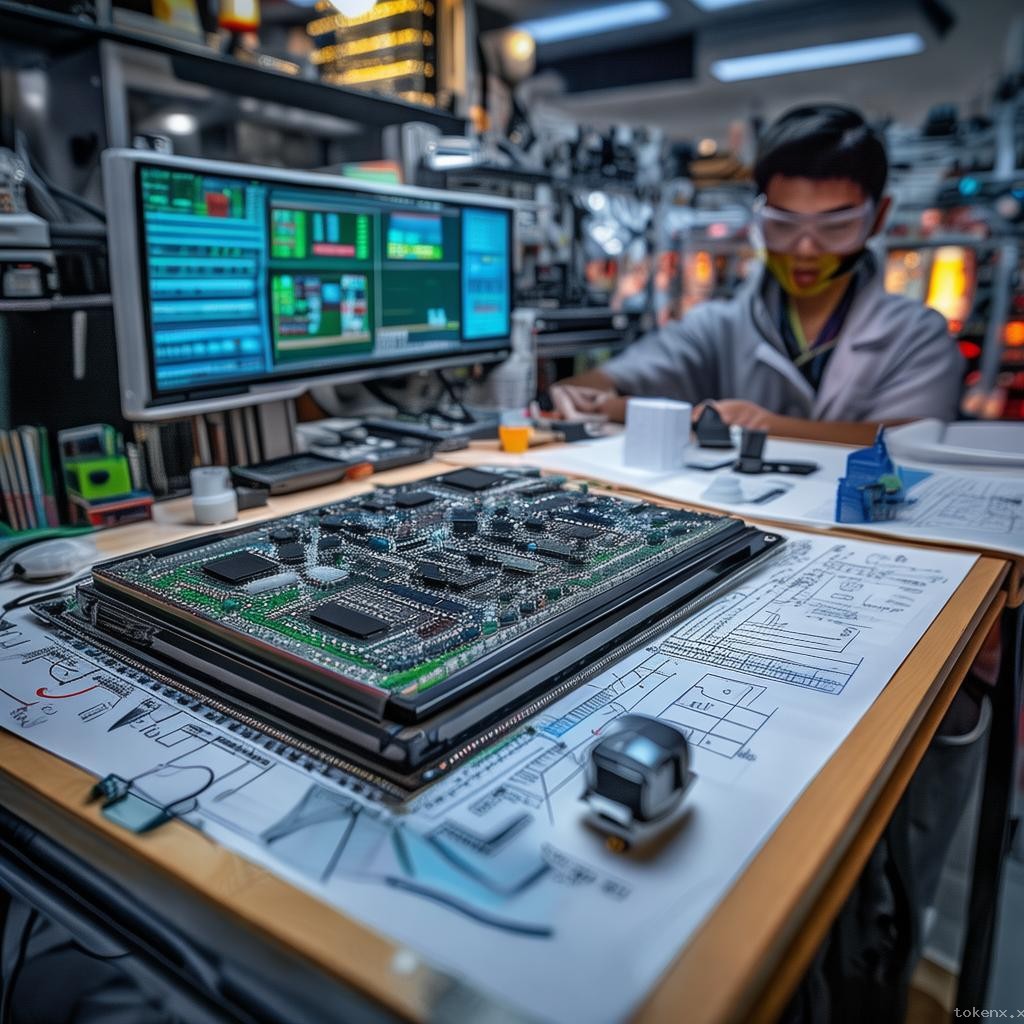

從零開始制作FPGA圖形加速器:探索GPU實(shí)現(xiàn)原理

一、引言:走進(jìn)FPGA與GPU的奇妙融合

在數(shù)字時(shí)代,圖形處理單元(GPU)已成為高性能計(jì)算和圖形渲染的核心。而現(xiàn)場(chǎng)可編程門陣列(FPGA)作為一種靈活的硬件平臺(tái),能夠根據(jù)需要定制計(jì)算邏輯,實(shí)現(xiàn)高效的硬件加速。將FPGA與GPU的理念相結(jié)合,我們可以從零開始,設(shè)計(jì)并實(shí)現(xiàn)一個(gè)屬于自己的圖形加速器,探索GPU背后的神秘面紗。

二、FPGA圖形加速器的基礎(chǔ)概念

1. FPGA簡(jiǎn)介

FPGA是一種可編程邏輯器件,通過內(nèi)部的可編程邏輯單元(LUT)、寄存器和I/O接口等資源,實(shí)現(xiàn)復(fù)雜的數(shù)字電路功能。與傳統(tǒng)的ASIC相比,F(xiàn)PGA具有更高的靈活性和可重構(gòu)性,能夠根據(jù)不同應(yīng)用需求進(jìn)行定制。

2. GPU與圖形加速

GPU是專為圖形渲染和高性能計(jì)算設(shè)計(jì)的處理器。它擁有大量的并行計(jì)算單元,能夠高效處理大規(guī)模數(shù)據(jù),實(shí)現(xiàn)快速的圖形渲染和計(jì)算加速。在基于FPGA的圖形加速器中,我們將利用FPGA的并行處理能力,模擬GPU的部分功能,實(shí)現(xiàn)硬件加速。

三、從零開始:FPGA圖形加速器的設(shè)計(jì)流程

1. 明確應(yīng)用場(chǎng)景與性能目標(biāo)

設(shè)計(jì)之初,我們首先需要明確FPGA圖形加速器的應(yīng)用場(chǎng)景,如游戲渲染、科學(xué)計(jì)算或嵌入式系統(tǒng)等。根據(jù)應(yīng)用場(chǎng)景,確定性能目標(biāo),包括計(jì)算能力、內(nèi)存帶寬、延遲等。這些目標(biāo)將直接影響后續(xù)架構(gòu)設(shè)計(jì)。

2. 架構(gòu)設(shè)計(jì)

在架構(gòu)設(shè)計(jì)階段,我們需要設(shè)計(jì)流處理器(Stream Processors, SPs)的數(shù)量、計(jì)算能力以及通信方式。流處理器是GPU的基本計(jì)算單元,類似于CPU中的核心。此外,還需設(shè)計(jì)多級(jí)緩存結(jié)構(gòu)、全局內(nèi)存、共享內(nèi)存和寄存器等存儲(chǔ)器層次結(jié)構(gòu),以及任務(wù)調(diào)度和負(fù)載均衡機(jī)制。

3. RTL設(shè)計(jì)與邏輯綜合

使用硬件描述語言(如Verilog或VHDL)進(jìn)行寄存器傳輸級(jí)(RTL)設(shè)計(jì),實(shí)現(xiàn)GPU的核心功能模塊。隨后,利用EDA工具進(jìn)行邏輯綜合、時(shí)序分析和布局布線,生成FPGA的物理實(shí)現(xiàn)。這一過程將抽象的硬件描述轉(zhuǎn)化為具體的電路布局。

4. 功能驗(yàn)證與測(cè)試

在FPGA圖形加速器設(shè)計(jì)完成后,我們需要進(jìn)行功能驗(yàn)證和測(cè)試。這包括單元測(cè)試、系統(tǒng)測(cè)試、功耗測(cè)試和熱測(cè)試等,以確保設(shè)計(jì)滿足需求和規(guī)格。通過不斷的調(diào)試和優(yōu)化,我們可以提高加速器的性能和穩(wěn)定性。

四、基于ZYNQ平臺(tái)的FPGA圖形加速器實(shí)現(xiàn)

為了更具體地展示FPGA圖形加速器的實(shí)現(xiàn)過程,我們將以ZYNQ平臺(tái)為例。ZYNQ是一款集成了ARM處理器和FPGA的片上系統(tǒng)(SoC),適用于高性能嵌入式系統(tǒng)設(shè)計(jì)。

1. ZYNQ平臺(tái)簡(jiǎn)介

ZYNQ平臺(tái)結(jié)合了處理系統(tǒng)(PS)和可編程邏輯(PL)兩部分。PS部分包含ARM處理器、內(nèi)存控制器和外設(shè)接口等,負(fù)責(zé)系統(tǒng)的控制和數(shù)據(jù)管理。PL部分則是FPGA資源,用于實(shí)現(xiàn)自定義的硬件加速功能。

2. 基于ZYNQ的FPGA圖形加速器實(shí)現(xiàn)步驟

- 環(huán)境搭建:首先,我們需要安裝Vivado和Vitis等開發(fā)工具,配置ZYNQ開發(fā)環(huán)境。

- 生成Platform:在Vivado中,通過導(dǎo)入ZYNQ硬件描述文件,生成Platform。Platform包含了PS和PL之間的接口定義和硬件資源分配。

- 設(shè)計(jì)硬件加速模塊:在Vivado HLS中,我們使用高層次綜合工具將C/C++代碼轉(zhuǎn)換為HDL代碼,設(shè)計(jì)硬件加速模塊。這些模塊將實(shí)現(xiàn)特定的圖形處理功能,如濾波、變換等。

- 集成與測(cè)試:將設(shè)計(jì)好的硬件加速模塊集成到Platform中,生成bit流文件。隨后,在Vitis中進(jìn)行軟件編程和系統(tǒng)集成,編寫測(cè)試代碼驗(yàn)證硬件加速功能。

- 程序固化與部署:最后,我們將生成的bit流文件和軟件程序固化到SPI Flash中,實(shí)現(xiàn)FPGA圖形加速器的部署。通過配置啟動(dòng)管腳,我們可以使ZYNQ平臺(tái)從QSPI Flash啟動(dòng),自動(dòng)加載并運(yùn)行圖形加速器。

五、性能優(yōu)化與持續(xù)改進(jìn)

在FPGA圖形加速器的實(shí)現(xiàn)過程中,性能優(yōu)化是一個(gè)持續(xù)的過程。我們可以通過以下方式提高加速器的性能:

- 優(yōu)化并行處理能力:充分利用FPGA的并行計(jì)算能力,設(shè)計(jì)高效的并行處理架構(gòu)。

- 優(yōu)化內(nèi)存訪問:通過設(shè)計(jì)合理的緩存結(jié)構(gòu)和內(nèi)存訪問策略,提高數(shù)據(jù)訪問速度和帶寬效率。

- 動(dòng)態(tài)電壓和頻率調(diào)節(jié):根據(jù)實(shí)際應(yīng)用需求,動(dòng)態(tài)調(diào)整FPGA的工作電壓和頻率,實(shí)現(xiàn)能效比的最優(yōu)化。

六、Q&A:初學(xué)者常見問題解答

Q1:FPGA與GPU有什么區(qū)別? A1:FPGA是一種可編程邏輯器件,具有高度的靈活性和可重構(gòu)性,能夠根據(jù)應(yīng)用需求進(jìn)行定制。而GPU是專為圖形渲染和高性能計(jì)算設(shè)計(jì)的處理器,擁有大量的并行計(jì)算單元。FPGA圖形加速器結(jié)合了FPGA的靈活性和GPU的并行處理能力,實(shí)現(xiàn)了高效的硬件加速。 Q2:基于FPGA的圖形加速器適用于哪些應(yīng)用場(chǎng)景? A2:基于FPGA的圖形加速器適用于多種應(yīng)用場(chǎng)景,如游戲渲染、科學(xué)計(jì)算、嵌入式系統(tǒng)等。在游戲渲染中,F(xiàn)PGA圖形加速器可以實(shí)現(xiàn)高效的圖形渲染和物理模擬。在科學(xué)計(jì)算中,它可以加速大規(guī)模數(shù)據(jù)的處理和分析。在嵌入式系統(tǒng)中,F(xiàn)PGA圖形加速器能夠提供更低的功耗和更高的性能。 Q3:如何開始學(xué)習(xí)FPGA圖形加速器的設(shè)計(jì)? A3:初學(xué)者可以從學(xué)習(xí)硬件描述語言(如Verilog或VHDL)開始,掌握基本的數(shù)字電路設(shè)計(jì)原理。隨后,可以學(xué)習(xí)FPGA開發(fā)工具(如Vivado)的使用,了解FPGA的設(shè)計(jì)流程和資源分配。通過參與實(shí)際項(xiàng)目或?qū)嶒?yàn),不斷積累經(jīng)驗(yàn),逐步深入FPGA圖形加速器的設(shè)計(jì)領(lǐng)域。

七、結(jié)語:探索未知,創(chuàng)造未來

從零開始制作一個(gè)基于FPGA的圖形加速器,是一次充滿挑戰(zhàn)與樂趣的旅程。在這個(gè)過程中,我們不僅學(xué)習(xí)了GPU的實(shí)現(xiàn)原理,還掌握了FPGA的設(shè)計(jì)方法和性能優(yōu)化技巧。未來,隨著技術(shù)的不斷進(jìn)步和應(yīng)用需求的不斷變化,我們可以繼續(xù)探索未知領(lǐng)域,創(chuàng)造更加高效、智能的圖形處理解決方案。

文章評(píng)論 (1)

發(fā)表評(píng)論