從零開始制作一個屬于你自己的GPU:基于FPGA的圖形加速器實現(xiàn)原理

引言

隨著大數(shù)據(jù)、人工智能和圖形處理技術(shù)的飛速發(fā)展,對高性能計算的需求日益增長。傳統(tǒng)CPU在圖形處理方面存在性能瓶頸,而GPU雖然性能強大,但其高昂的成本和定制化限制也讓許多開發(fā)者望而卻步。在此背景下,基于FPGA(現(xiàn)場可編程門陣列)的圖形加速器應(yīng)運而生,為圖形處理領(lǐng)域帶來了新的解決方案。

FPGA在圖形處理中的優(yōu)勢

FPGA作為一種半定制集成電路,具有高度的靈活性和可編程性,能夠針對特定應(yīng)用進行優(yōu)化。在圖形處理領(lǐng)域,F(xiàn)PGA的優(yōu)勢主要體現(xiàn)在以下幾個方面:

- 并行處理能力:FPGA內(nèi)部包含大量的邏輯單元和布線資源,支持高度并行處理,能夠顯著提升圖形處理速度。

- 低功耗:相比GPU,F(xiàn)PGA在功耗方面具有明顯優(yōu)勢,尤其適合對能耗有嚴(yán)格要求的場景。

- 小型化:FPGA可以實現(xiàn)高度集成,減小設(shè)備體積,降低制造成本。

- 可定制性:FPGA允許開發(fā)者根據(jù)實際需求進行定制設(shè)計,實現(xiàn)硬件加速功能的最大化利用。

基于FPGA的圖形加速器設(shè)計流程

1. 需求分析與架構(gòu)設(shè)計

在設(shè)計之初,首先需要明確加速器的應(yīng)用場景和需求,如圖像處理、視頻編碼、深度學(xué)習(xí)等。根據(jù)需求,設(shè)計合理的架構(gòu),包括輸入/輸出接口、處理單元、存儲模塊等。

2. 模塊劃分與實現(xiàn)

將整體架構(gòu)劃分為多個功能模塊,如卷積模塊、池化模塊、激活函數(shù)模塊等。針對每個模塊,利用Verilog或VHDL等硬件描述語言進行具體實現(xiàn)。例如,在卷積模塊中,需要設(shè)計高效的卷積運算單元,支持多種卷積核大小和步長。

3. 流水線設(shè)計與優(yōu)化

為了提高處理速度,采用深度流水線設(shè)計,將各個模塊的操作劃分為多個時鐘周期執(zhí)行。同時,通過優(yōu)化數(shù)據(jù)路徑、減少冗余操作等方式,進一步提升加速器性能。

4. 驗證與測試

在完成設(shè)計后,需要進行嚴(yán)格的驗證和測試,確保加速器功能的正確性和穩(wěn)定性。這包括仿真測試、硬件在環(huán)測試等多個環(huán)節(jié)。

關(guān)鍵技術(shù)分析

1. 卷積神經(jīng)網(wǎng)絡(luò)加速

卷積神經(jīng)網(wǎng)絡(luò)(CNN)在圖像處理領(lǐng)域具有廣泛應(yīng)用。基于FPGA的CNN加速器通過并行處理多個卷積核,實現(xiàn)高效的特征提取和分類。例如,可以采用脈動陣列結(jié)構(gòu),將卷積運算映射到FPGA的二維邏輯單元上,實現(xiàn)高速并行計算。

2. 數(shù)據(jù)存儲與訪問優(yōu)化

圖形處理涉及大量的數(shù)據(jù)讀寫操作,如何高效管理存儲資源成為關(guān)鍵。通過設(shè)計合理的緩存結(jié)構(gòu)、采用直接內(nèi)存訪問(DMA)等方式,可以有效降低存儲訪問延遲,提高數(shù)據(jù)吞吐量。

3. 動態(tài)可重構(gòu)性

FPGA的動態(tài)可重構(gòu)性使其能夠根據(jù)不同應(yīng)用場景靈活調(diào)整硬件資源。例如,在圖形處理任務(wù)發(fā)生變化時,可以通過重新配置FPGA內(nèi)部邏輯,實現(xiàn)硬件加速功能的快速切換。

行業(yè)趨勢分析

- 異構(gòu)計算融合:未來,F(xiàn)PGA將與CPU、GPU等異構(gòu)計算資源更加緊密地融合,形成更加高效、靈活的計算體系。

- AI加速應(yīng)用:隨著人工智能技術(shù)的不斷發(fā)展,基于FPGA的AI加速器將在更多領(lǐng)域得到應(yīng)用,如自動駕駛、醫(yī)療影像分析等。

- 低功耗設(shè)計:在物聯(lián)網(wǎng)、移動設(shè)備等對能耗有嚴(yán)格要求的場景下,低功耗設(shè)計將成為FPGA圖形加速器的重要發(fā)展方向。

專業(yè)見解與預(yù)測

- 定制化趨勢加強:針對不同應(yīng)用場景的定制化FPGA圖形加速器將更加普及,以滿足用戶對高性能、低功耗、小體積的多元化需求。

- 軟件與硬件協(xié)同設(shè)計:未來,軟件與硬件的協(xié)同設(shè)計將成為主流趨勢,通過更加緊密的軟硬件結(jié)合,實現(xiàn)更加高效、可靠的圖形處理解決方案。

- 開源生態(tài)構(gòu)建:隨著開源文化的興起,基于FPGA的圖形加速器開源生態(tài)將逐漸完善,為開發(fā)者提供更加便捷、豐富的開發(fā)資源和工具。

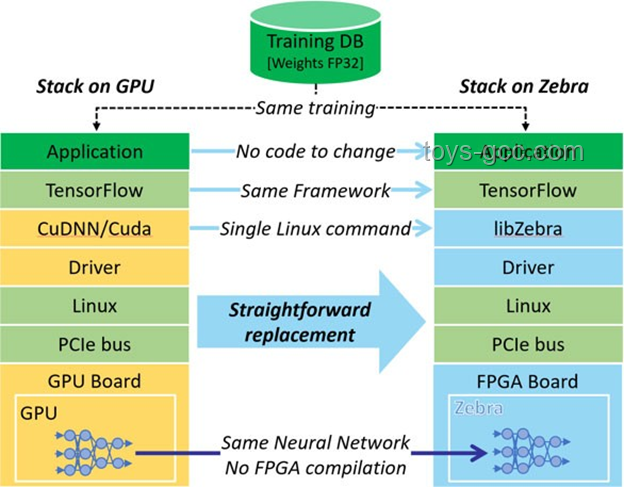

圖表說明(示例)

圖1:FPGA內(nèi)部架構(gòu)圖,展示了邏輯單元、布線資源等關(guān)鍵組件。

常見問答(Q&A)

Q1:基于FPGA的圖形加速器與傳統(tǒng)GPU相比有哪些優(yōu)勢? A1:基于FPGA的圖形加速器在功耗、體積、可定制性等方面具有明顯優(yōu)勢,尤其適合對能耗有嚴(yán)格要求或需要高度定制化的應(yīng)用場景。 Q2:設(shè)計基于FPGA的圖形加速器需要掌握哪些關(guān)鍵技術(shù)? A2:設(shè)計基于FPGA的圖形加速器需要掌握卷積神經(jīng)網(wǎng)絡(luò)加速、數(shù)據(jù)存儲與訪問優(yōu)化、動態(tài)可重構(gòu)性等關(guān)鍵技術(shù)。 通過以上分析,我們可以看到,基于FPGA的圖形加速器在實現(xiàn)高性能、低功耗、小體積的圖形處理解決方案方面具有巨大潛力。隨著技術(shù)的不斷發(fā)展,未來基于FPGA的圖形加速器將在更多領(lǐng)域得到廣泛應(yīng)用,為圖形處理領(lǐng)域帶來新的變革。

文章評論 (2)

發(fā)表評論