從零開始制作屬于你自己的GPU:基于FPGA的圖形加速器實現原理

一、引言與目標

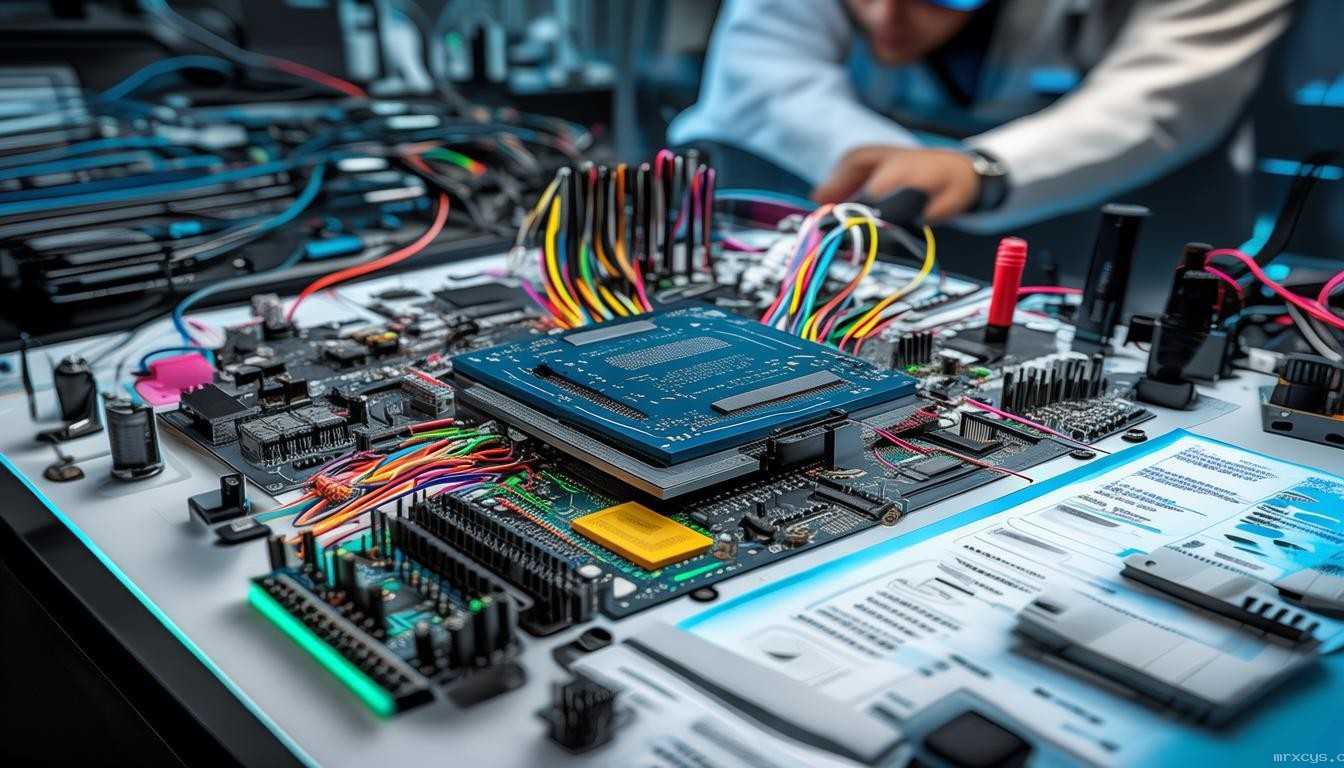

在現代計算系統中,GPU因其高效的并行處理能力,成為圖形渲染和科學計算等領域的關鍵組件。通過基于FPGA設計和實現一個圖形加速器,你不僅能夠掌握硬件設計的全過程,還能更好地理解GPU的工作原理。本指南的目標是通過一系列步驟,指導你完成一個基本圖形加速器的設計和實現。

二、準備工作

2.1 硬件與軟件環境

- 硬件:FPGA開發板(如Xilinx ZedBoard或Intel Cyclone V),HDMI顯示接口,必要的連接線。

- 軟件:FPGA開發軟件(如Vivado),仿真工具(如ModelSim),Verilog編譯器,HDMI信號發生器庫。

2.2 基礎知識

- 熟悉FPGA的基本結構和工作原理。

- 掌握Verilog硬件描述語言的基礎語法。

- 了解基本的圖像處理算法。

三、設計框架與功能規劃

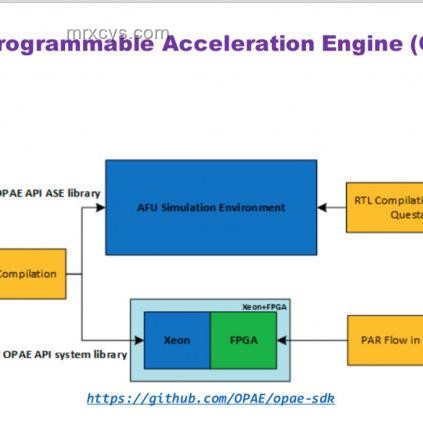

3.1 設計框架

基于FPGA的圖形加速器主要包括以下幾個模塊:

- 輸入接口:接收圖像數據或圖形命令。

- 像素處理單元:對圖像進行渲染或變換處理。

- 幀緩沖區:存儲待顯示的圖像數據。

- 輸出接口:將處理后的圖像數據通過HDMI輸出到顯示器。

3.2 功能規劃

- 基本渲染功能:實現簡單的像素繪制和填充。

- 圖像處理功能:如邊緣檢測、圖像縮放等。

- 高性能輸出:通過HDMI接口實現高幀率圖像顯示。

四、詳細設計與實現

4.1 輸入接口設計

輸入接口模塊負責接收來自CPU或其他設備的圖像數據或圖形命令。可以使用AXI總線等標準接口協議,確保數據傳輸的效率和可靠性。

module InputInterface ( input wire clk, input wire rst, // AXI總線接口信號 output reg [31:0] pixel_data, output reg pixel_valid // 實現AXI總線接口邏輯 endmodule4.2 像素處理單元設計

像素處理單元是圖形加速器的核心,負責執行各種圖形渲染和圖像處理算法。可以使用流水線結構來提高處理效率。

module PixelProcessingUnit ( input wire clk, input wire rst, input wire [31:0] pixel_in, input wire pixel_in_valid, output reg [31:0] pixel_out, output reg pixel_out_valid // 實現像素處理邏輯,如顏色變換、邊緣檢測等 endmodule4.3 幀緩沖區設計

幀緩沖區用于存儲待顯示的圖像數據。考慮到內存訪問效率和圖像分辨率,可以使用雙緩沖結構。

module FrameBuffer ( input wire clk, input wire rst, input wire [31:0] pixel_data, input wire pixel_write, input wire [15:0] x, input wire [15:0] y, output reg [31:0] pixel_read_data, input wire [15:0] read_x, input wire [15:0] read_y, output reg pixel_read_valid // 實現幀緩沖區讀寫邏輯 endmodule4.4 輸出接口設計

輸出接口模塊負責將處理后的圖像數據通過HDMI接口輸出到顯示器。需要實現HDMI協議中的TMDS(Transition Minimized Differential Signaling)編碼和時鐘生成。

module OutputInterface ( input wire clk, input wire rst, input wire [31:0] pixel_data, input wire pixel_valid, // HDMI接口信號 // 實現HDMI TMDS編碼和時鐘生成邏輯 endmodule五、系統集成與測試

5.1 系統集成

將各個模塊按照設計框架進行集成,形成完整的圖形加速器系統。注意模塊間的信號連接和時鐘同步。

5.2 仿真與調試

使用ModelSim等仿真工具對系統進行仿真,驗證各模塊的功能和相互間的協作。仿真過程中可以加入測試向量,觀察輸出是否符合預期。

5.3 硬件調試與驗證

將設計下載到FPGA開發板上,通過HDMI接口連接顯示器進行硬件調試。觀察顯示效果,調整參數以優化性能。

六、實用技巧與竅門

- 模塊化設計:將系統劃分為多個獨立模塊,便于調試和維護。

- 流水線技術:在像素處理單元中使用流水線結構,提高處理效率。

- 雙緩沖技術:在幀緩沖區中使用雙緩沖結構,減少屏幕閃爍。

- HDMI協議理解:深入理解HDMI協議,確保信號傳輸的正確性和穩定性。

七、常見問題解答(FAQ)

- Q1:如何處理不同分辨率的圖像? A1:可以通過調整幀緩沖區的大小和像素處理單元中的縮放算法來適應不同分辨率的圖像。

- Q2:如何優化系統性能? A2:可以通過優化像素處理單元的算法、使用更高效的內存訪問模式、調整時鐘頻率等方法來提高系統性能。

- Q3:如何調試HDMI信號問題?

A3:可以使用示波器或邏輯分析儀檢測HDMI信號的質量和時序,確保信號符合HDMI協議標準。

八、實際案例與示例

以下是一個簡單的示例,展示如何在FPGA上實現一個基本的像素繪制功能。

module SimplePixelDrawer ( input wire clk, input wire rst, input wire [15:0] x, input wire [15:0] y, input wire [31:0] color, input wire draw, // HDMI接口信號(簡化) output reg [23:0] hdmi_data, output reg hdmi_hsync, output reg hdmi_vsync // 幀緩沖區(簡化) reg [31:0] frame_buffer [1023:0][767:0]; // 像素繪制邏輯 always @(posedge clk or posedge rst) begin if (rst) begin // 復位幀緩沖區 end else if (draw) begin frame_buffer[y][x] <= color; end end // HDMI輸出邏輯(簡化) endmodule在上述示例中,

SimplePixelDrawer模塊接收像素坐標、顏色和繪制命令,將指定顏色的像素繪制到幀緩沖區中,并通過HDMI接口輸出到顯示器。九、總結與展望

通過本指南的學習和實踐,你已經掌握了基于FPGA設計和實現圖形加速器的基本原理和方法。未來,你可以進一步探索更復雜的圖形渲染算法、優化系統性能、擴展功能等方向,不斷提升自己的硬件設計和FPGA編程能力。希望本指南能夠對你的學習和實踐有所幫助! (注:由于篇幅限制,本指南中的代碼示例和模塊設計均進行了簡化。在實際項目中,需要根據具體需求和FPGA資源情況進行詳細設計和優化。)

文章評論 (5)

發表評論