從零開(kāi)始制作FPGA圖形加速器

一、引言:圖形加速器的魅力

在現(xiàn)代計(jì)算機(jī)系統(tǒng)中,圖形加速器扮演著至關(guān)重要的角色。它們以圖形加速卡的形式出現(xiàn),專(zhuān)門(mén)負(fù)責(zé)圖形運(yùn)算,使得圖像處理、三維游戲等任務(wù)變得流暢而高效。想象一下,如果沒(méi)有圖形加速器,我們的電腦在處理復(fù)雜圖形時(shí)可能會(huì)變得異常緩慢,體驗(yàn)大打折扣。而現(xiàn)在,我們將從零開(kāi)始,利用FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)技術(shù),親手制作一個(gè)圖形加速器,是不是既有趣又充滿(mǎn)挑戰(zhàn)呢?

二、FPGA與圖形加速器的基礎(chǔ)

1. FPGA是什么?

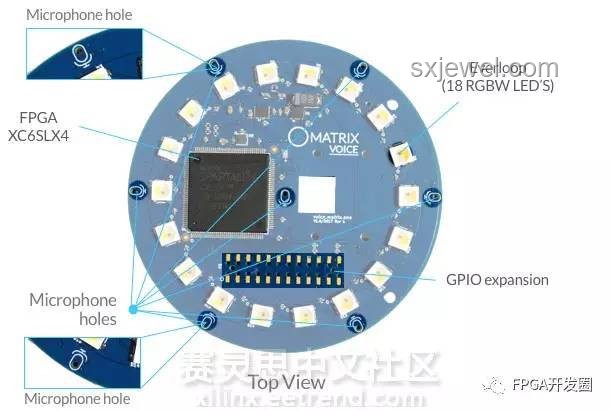

FPGA,即現(xiàn)場(chǎng)可編程門(mén)陣列,是一種半定制集成電路。它內(nèi)部包含了大量的邏輯單元和布線(xiàn)資源,用戶(hù)可以通過(guò)編程來(lái)配置這些資源,實(shí)現(xiàn)特定的功能。FPGA因其并行處理、速度快、功耗低、小型化等優(yōu)勢(shì),在許多領(lǐng)域都有著廣泛的應(yīng)用。

2. 圖形加速器的核心功能

圖形加速器的主要任務(wù)是從CPU中接過(guò)圖形的處理工作,自己處理圖形的渲染、變換等復(fù)雜計(jì)算。這樣不僅能減輕CPU的負(fù)擔(dān),還能大大提高圖形處理的效率。一個(gè)典型的圖形加速器包含圖形加速芯片、內(nèi)存、數(shù)模轉(zhuǎn)換器等關(guān)鍵元件。

三、基于FPGA的圖形加速器設(shè)計(jì)

1. 設(shè)計(jì)思路

基于FPGA的圖形加速器設(shè)計(jì),關(guān)鍵在于如何高效地利用FPGA的資源來(lái)實(shí)現(xiàn)圖形處理的功能。我們需要考慮如何配置FPGA的邏輯單元和布線(xiàn)資源,以實(shí)現(xiàn)圖形的渲染、變換、裁剪等操作。同時(shí),還需要優(yōu)化存儲(chǔ)訪問(wèn),提高數(shù)據(jù)處理的效率。

2. 流水線(xiàn)結(jié)構(gòu)設(shè)計(jì)

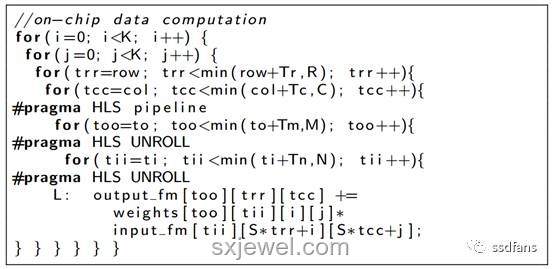

在圖形處理中,流水線(xiàn)技術(shù)是一種常用的并行處理策略。通過(guò)將圖形處理的任務(wù)分解為多個(gè)階段,每個(gè)階段并行處理不同的數(shù)據(jù),可以大大提高處理速度。在FPGA圖形加速器中,我們可以設(shè)計(jì)深度流水線(xiàn)結(jié)構(gòu),將圖形的渲染、變換等操作分解為多個(gè)流水線(xiàn)階段,每個(gè)階段利用FPGA的邏輯單元進(jìn)行并行處理。

3. 存儲(chǔ)訪問(wèn)優(yōu)化

存儲(chǔ)訪問(wèn)是圖形處理中的一個(gè)重要環(huán)節(jié)。為了提高存儲(chǔ)訪問(wèn)的效率,我們需要優(yōu)化FPGA的片上存儲(chǔ)和片外存儲(chǔ)的使用。片上存儲(chǔ)(如BRAM)具有高帶寬和低延遲的特點(diǎn),我們應(yīng)該盡可能地將常用的數(shù)據(jù)存放在片上存儲(chǔ)中。同時(shí),還需要設(shè)計(jì)合理的訪存策略,減少片外存儲(chǔ)的訪問(wèn)次數(shù)和延遲。

四、卷積神經(jīng)網(wǎng)絡(luò)加速器案例

為了更具體地說(shuō)明基于FPGA的圖形加速器的實(shí)現(xiàn)原理,我們以卷積神經(jīng)網(wǎng)絡(luò)(CNN)加速器為例進(jìn)行介紹。

1. CNN的基本概念

卷積神經(jīng)網(wǎng)絡(luò)是一種非常典型的前向傳播神經(jīng)網(wǎng)絡(luò),特別適合于二維數(shù)據(jù)處理的應(yīng)用場(chǎng)景。它包含輸入層、輸出層和隱含層。其中,隱含層通常由交替出現(xiàn)的卷積層和池化層組成。卷積層負(fù)責(zé)提取圖像的特征,而池化層則用于逐步壓縮神經(jīng)元和權(quán)值數(shù)量。

2. CNN加速器的FPGA實(shí)現(xiàn)

在FPGA上實(shí)現(xiàn)CNN加速器,我們需要充分利用CNN的高度并行性。具體來(lái)說(shuō),可以針對(duì)CNN的五層結(jié)構(gòu)(輸入層、第一次卷積層C1、第一次池化層S2、第二次卷積層C3、第二次池化層S4和全連接輸出層O5)進(jìn)行流水線(xiàn)設(shè)計(jì)和并行處理。

- 輸入層與卷積層C1:將輸入的二維圖像轉(zhuǎn)換為一維向量,并利用FPGA的移位寄存器和FIFO(先進(jìn)先出隊(duì)列)實(shí)現(xiàn)數(shù)據(jù)的緩存和流水處理。卷積運(yùn)算可以通過(guò)配置FPGA的邏輯單元來(lái)實(shí)現(xiàn),每個(gè)卷積核對(duì)應(yīng)一個(gè)卷積運(yùn)算單元。

- 池化層S2:池化操作可以通過(guò)對(duì)緩存的數(shù)據(jù)進(jìn)行分組,并利用FPGA的邏輯單元進(jìn)行并行處理來(lái)實(shí)現(xiàn)。常用的池化方式有最大值池化和均值池化。

- 卷積層C3與池化層S4:與C1和S2類(lèi)似,但需要注意的是,C3層的輸入來(lái)自S2層的多個(gè)特征圖,因此需要進(jìn)行多通道并行處理。

- 全連接輸出層O5:將S4層的輸出展成一維向量,并通過(guò)權(quán)重矩陣實(shí)現(xiàn)全連接。這一層可以利用FPGA的BRAM來(lái)存儲(chǔ)權(quán)重矩陣和中間結(jié)果,以提高處理速度。

通過(guò)這樣的設(shè)計(jì),我們可以充分利用FPGA的并行處理能力和存儲(chǔ)資源,實(shí)現(xiàn)高效的CNN加速。

五、常見(jiàn)問(wèn)答

Q1:FPGA與GPU在圖形處理上有什么區(qū)別? A1:FPGA和GPU在圖形處理上各有優(yōu)勢(shì)。GPU是專(zhuān)門(mén)為圖形處理而設(shè)計(jì)的處理器,具有高度的并行性和強(qiáng)大的計(jì)算能力。而FPGA則是一種半定制集成電路,用戶(hù)可以通過(guò)編程來(lái)配置其資源,實(shí)現(xiàn)特定的功能。FPGA在靈活性、功耗和定制化方面更具優(yōu)勢(shì),但在通用計(jì)算能力上可能不如GPU。 Q2:基于FPGA的圖形加速器適用于哪些場(chǎng)景? A2:基于FPGA的圖形加速器適用于需要高效圖形處理和低功耗的應(yīng)用場(chǎng)景。例如,在深度學(xué)習(xí)、圖像處理、嵌入式系統(tǒng)等領(lǐng)域,F(xiàn)PGA圖形加速器可以發(fā)揮重要作用。此外,由于FPGA的可重構(gòu)性,它還可以根據(jù)不同的應(yīng)用需求進(jìn)行定制和優(yōu)化。

六、結(jié)語(yǔ):開(kāi)啟硬件設(shè)計(jì)的新篇章

從零開(kāi)始制作一個(gè)基于FPGA的圖形加速器是一項(xiàng)既有趣又充滿(mǎn)挑戰(zhàn)的任務(wù)。通過(guò)深入了解FPGA的原理和圖形處理的知識(shí),我們可以設(shè)計(jì)出高效的圖形加速器,為深度學(xué)習(xí)、圖像處理等領(lǐng)域提供強(qiáng)大的計(jì)算支持。希望本文能激發(fā)你對(duì)硬件設(shè)計(jì)的興趣,開(kāi)啟你的硬件設(shè)計(jì)之旅!

文章評(píng)論 (2)

發(fā)表評(píng)論