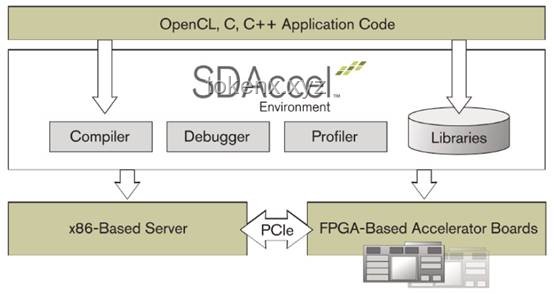

從零開始制作一個屬于你自己的GPU:基于FPGA的圖形加速器實現(xiàn)原理

一、引言:GPU與FPGA的邂逅

在現(xiàn)代計算機的世界里,GPU(圖形處理單元)和FPGA(現(xiàn)場可編程門陣列)都扮演著舉足輕重的角色。GPU擅長處理大規(guī)模并行計算任務(wù),比如圖形渲染、視頻編碼解碼等;而FPGA則以其高度的靈活性和可定制性,在硬件加速、信號處理等領(lǐng)域大放異彩。你有沒有想過,如果能將兩者的優(yōu)勢結(jié)合起來,從零開始制作一個屬于自己的GPU,會是一件多么酷炫的事情?

二、FPGA:可編程的硬件積木

2.1 FPGA是什么?

想象一下,你有一堆樂高積木,可以自由地搭建出各種形狀和結(jié)構(gòu)的玩具。FPGA就是這樣一個“硬件樂高”,它內(nèi)部包含大量的邏輯單元、連線資源和可編程的輸入輸出接口。你可以通過編程,將這些單元和接口按照你的需求連接起來,形成各種復(fù)雜的電路結(jié)構(gòu)。

2.2 FPGA的工作原理

FPGA的工作原理基于一種叫做“查找表”(Look-Up Table, LUT)的結(jié)構(gòu)。簡單來說,每個LUT就是一個小的存儲器,它存儲了輸入信號對應(yīng)的輸出信號。當FPGA接收到輸入信號時,它會查找相應(yīng)的LUT,然后輸出預(yù)先計算好的結(jié)果。這種機制使得FPGA能夠以極高的速度執(zhí)行復(fù)雜的邏輯運算。

2.3 FPGA的優(yōu)勢

- 靈活性:FPGA的硬件功能可以通過編程來改變,這意味著你可以隨時根據(jù)需求調(diào)整它的功能。

- 并行處理:FPGA能夠同時處理多個任務(wù),這在圖形處理和信號處理等領(lǐng)域非常有用。

- 低功耗:相比傳統(tǒng)的ASIC(專用集成電路),F(xiàn)PGA在達到同樣性能的情況下,通常能夠消耗更少的電力。

三、GPU:圖形處理的藝術(shù)

3.1 GPU的結(jié)構(gòu)

GPU是專門為圖形處理而設(shè)計的處理器。它內(nèi)部包含大量的核心(Core),每個核心都能獨立地執(zhí)行運算任務(wù)。這些核心被組織成多個流處理器(Stream Processor)或計算單元(Compute Unit),能夠并行地處理大量的數(shù)據(jù)。

3.2 GPU的工作原理

當GPU接收到圖形渲染任務(wù)時,它會將任務(wù)分解成許多小的計算任務(wù),并將這些任務(wù)分配給不同的核心去執(zhí)行。由于GPU內(nèi)部核心數(shù)量眾多,它能夠以極高的速度完成這些計算任務(wù),從而實現(xiàn)流暢的圖形渲染效果。

3.3 GPU的應(yīng)用

除了圖形渲染外,GPU還被廣泛應(yīng)用于深度學(xué)習(xí)、數(shù)據(jù)挖掘、物理模擬等領(lǐng)域。這些應(yīng)用都需要處理大量的數(shù)據(jù),并且需要高度的并行計算能力,這正是GPU所擅長的。

四、從零開始:基于FPGA的GPU實現(xiàn)原理

4.1 確定設(shè)計目標

在開始設(shè)計之前,你需要明確你的GPU需要實現(xiàn)哪些功能。比如,你是希望它能夠處理簡單的二維圖形渲染,還是希望它能夠支持復(fù)雜的三維圖形渲染?這些需求將直接影響你的設(shè)計方案和FPGA資源的分配。

4.2 設(shè)計硬件架構(gòu)

一旦確定了設(shè)計目標,你就可以開始設(shè)計GPU的硬件架構(gòu)了。這包括確定核心數(shù)量、流水線結(jié)構(gòu)、內(nèi)存訪問方式等。在這個過程中,你需要充分利用FPGA的靈活性和并行處理能力,來設(shè)計出一個高效且可擴展的硬件架構(gòu)。

4.3 編寫HDL代碼

接下來,你需要使用硬件描述語言(HDL)來編寫FPGA的配置代碼。常用的HDL包括VHDL和Verilog。這些代碼將描述GPU的內(nèi)部結(jié)構(gòu)和行為,包括各個模塊之間的連接關(guān)系、數(shù)據(jù)流的處理方式等。 舉個簡單的例子,假設(shè)你想要設(shè)計一個簡單的二維圖形渲染器。你可以使用Verilog編寫一個模塊,該模塊接收來自CPU的圖形數(shù)據(jù)(比如像素顏色和位置),然后將這些數(shù)據(jù)輸出到顯示器上。在這個模塊中,你需要定義輸入和輸出端口、內(nèi)部寄存器和狀態(tài)機等元素,并編寫相應(yīng)的邏輯代碼來實現(xiàn)圖形渲染的功能。

4.4 仿真與驗證

在編寫完HDL代碼后,你需要進行仿真和驗證工作。這包括使用仿真工具來模擬FPGA的運行情況,并檢查代碼是否滿足設(shè)計要求。如果發(fā)現(xiàn)問題或錯誤,你需要返回修改HDL代碼,直到仿真結(jié)果符合預(yù)期為止。

4.5 燒錄與測試

最后一步是將經(jīng)過驗證的HDL代碼燒錄到FPGA中,并進行實際的測試。你可以使用FPGA開發(fā)板來搭建測試環(huán)境,并將你的GPU連接到顯示器和其他外設(shè)上進行測試。通過觀察測試結(jié)果和調(diào)試信息,你可以進一步優(yōu)化你的設(shè)計并提高性能。

五、常見問答(Q&A)

Q1:FPGA和ASIC有什么區(qū)別? A1:FPGA是可編程的硬件,它的功能可以通過編程來改變;而ASIC是專用的集成電路,它的功能是固定的,并且是針對特定應(yīng)用而設(shè)計的。因此,F(xiàn)PGA在靈活性方面優(yōu)于ASIC,但在性能和功耗方面可能稍遜一籌。 Q2:為什么選擇FPGA來實現(xiàn)GPU? A2:FPGA的高度靈活性和并行處理能力使得它成為實現(xiàn)GPU的理想選擇。通過編程FPGA,你可以自由地設(shè)計GPU的內(nèi)部結(jié)構(gòu)和行為,以滿足不同的應(yīng)用需求。同時,F(xiàn)PGA的并行處理能力也能夠滿足GPU對高性能計算的需求。 Q3:從零開始制作GPU需要哪些技能? A3:從零開始制作GPU需要具備一定的硬件設(shè)計基礎(chǔ)、數(shù)字電路知識和編程能力。你需要熟悉FPGA的工作原理和HDL編程語言(如Verilog或VHDL),并具備一定的系統(tǒng)設(shè)計和調(diào)試經(jīng)驗。此外,你還需要了解圖形處理的基本原理和算法,以便能夠設(shè)計出高效的GPU架構(gòu)。

六、結(jié)語

從零開始制作一個屬于自己的GPU,雖然聽起來像是一個艱巨的任務(wù),但通過學(xué)習(xí)和實踐,你完全可以實現(xiàn)這個目標。FPGA作為一個強大的硬件設(shè)計平臺,為你提供了無限的想象空間和實踐機會。希望本文能夠為你提供一個清晰的思路和方向,讓你在探索GPU設(shè)計的道路上更加堅定和自信。

文章評論 (4)

發(fā)表評論